# クラス結合とブロック境界予測に基づいたHEVCのハードウェア向けSAOアルゴリズム

裴振宇 池永研究室 修士課程修了

## 研究背景・目的

- High Efficiency Video Coding(HEVC)

- 高品質・高精細映像(8Kx4K)

- Full HDの16倍画素数

- ハードウェアでの実現は不可欠

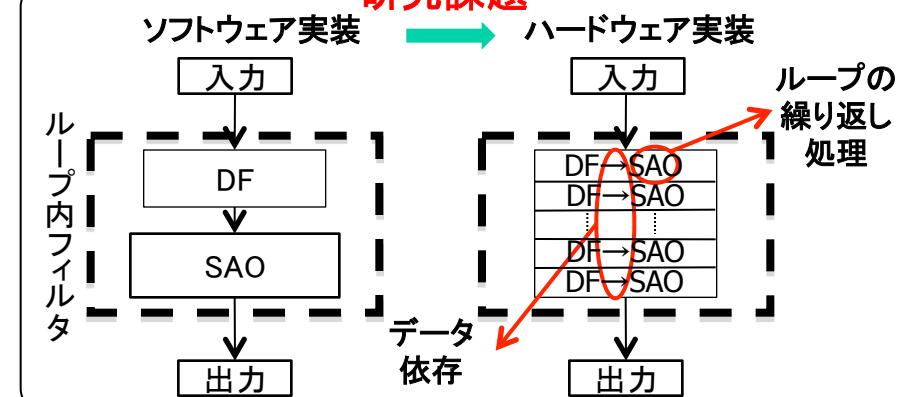

- データ依存

- 低演算アルゴリズム

10倍の演算量を

2倍の圧縮率で圧縮

演算量削減

ループ内フィルタの並列化

## 研究課題

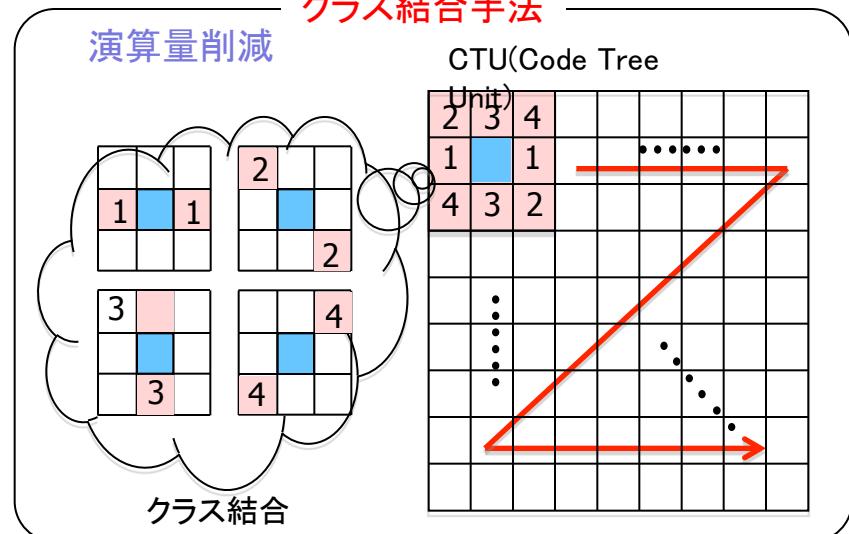

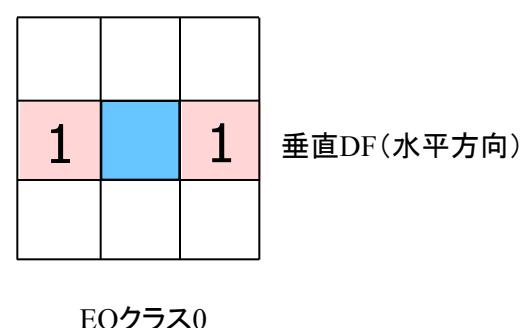

## クラス結合手法

### 演算量削減

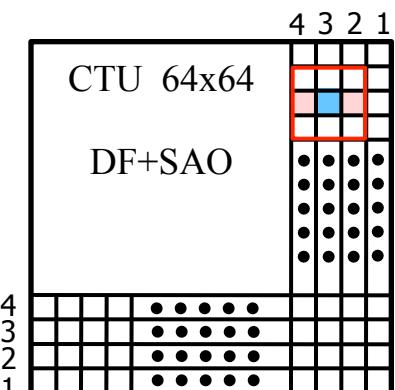

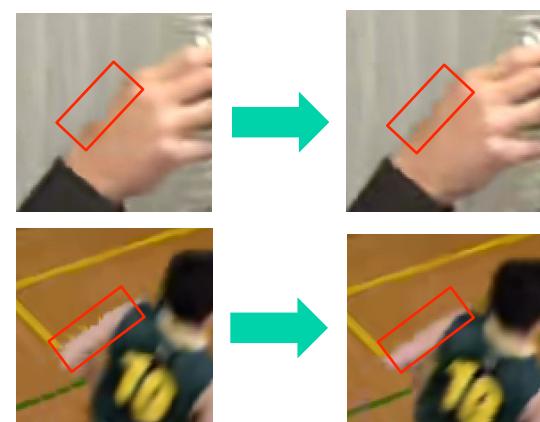

## ブロック境界予測手法

### ループ内フィルタの並列化

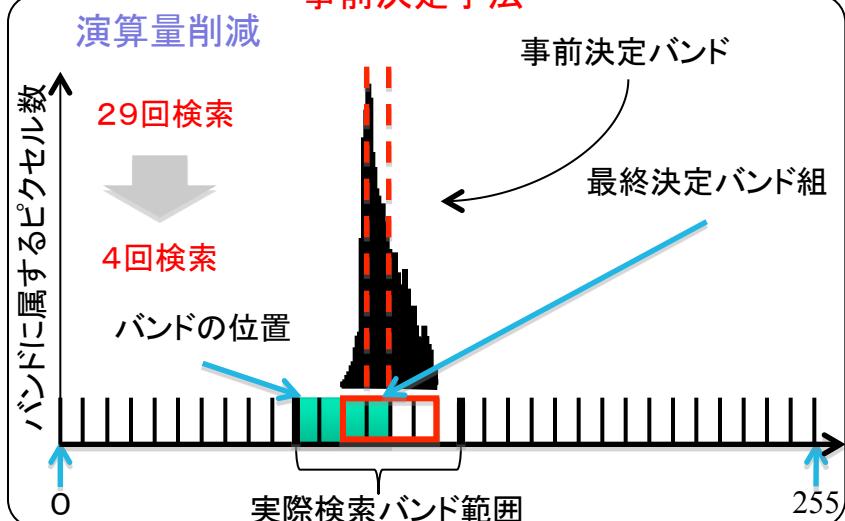

## 事前決定手法

## 実験結果

|                           | BD-bitrate<br>[%] | PSNR<br>[dB] | 処理時間<br>削減率[%] |

|---------------------------|-------------------|--------------|----------------|

| クラス結合<br>事前決定<br>ブロック境界予測 | 0.008333          | 0.001328     | 31.27          |

| クラス結合<br>ブロック境界予測         | -0.17             | 0.00425      | 21.51          |

提案

手法

早稲田大学大学院情報生産システム研究科